TECHNICAL BLOG

Thermal capacity mapping of cryogenic platforms for quantum computers

- Fault tolerant quantum computing will require large-scale cryogenic input-output (IO) infrastructures, which are complex to design, model and validate.

- We have demonstrated a novel approach to understanding cryogenic platforms and how the IO infrastructure affects the platform performance, referred to as platform capacity mapping.

- This approach can be used as tooling towards optimising system design as well as predicting how an arbitrary IO infrastructure will affect the platform.

- A key extension of this work is applying capacity mapping to more platforms, to understand its utility better and investigate platform-to-platform variance, as well as further verification of its predictive capability with larger validation payloads.

Scott Manifold

QUANTUM ENGINEER

Scott completed his PhD at Cardiff University working in the Cardiff Diamond Foundry where he gained experience in quantum device development. This included nanofabrication and low temperature RF and DC characterisation of superconducting diamond Josephson junctions and co-planar resonators. At OQC, he specialises in the research and development of next generation cryogenic input-output technologies and their integration into dilution refrigerators.

George Long

SENIOR QUANTUM ENGINEER

George leads the cryogenic infrastructure team within OQC’s advanced product development group. George’s responsibilities include the specification of the cryogenic measurement infrastructure for production systems and driving long term development work towards scaling this infrastructure to support future OQC quantum computers. Prior to joining OQC, George worked at the National Physical Laboratory (NPL) across the Quantum Information Processing group and the Quantum Material and Sensors group. George was involved in multiple research projects involving the design and measurement of various quantum sensors for single particle metrology, including Josephson junction and Superconducting Quantum Interference Device (SQUID) based radio-frequency electronics, collaborating with numerous universities and national measurement institutes over the course of his tenure.

As quantum computing scales towards practical computation and the essential threshold for unlocking real-world applications, we encounter a variety of scaling challenges, with areas across the computing stack requiring extensive research and development. A key area of focus is the increasing complexity of the cryogenic infrastructure of a quantum computer. Along with many other quantum computing technologies, the superconducting circuits in our devices require cryogenic temperatures in order to operate. We achieve this by enclosing the superconducting circuits in a cryogenic platform: a large dilution refrigerator, which cools the device close to absolute zero through the use of liquid helium.

Why do quantum computers require such cold temperatures?

Despite their enormous power that is derived from the interaction of different qubits, quantum states are very fragile and can only exist at incredibly low temperatures. Maintaining their quantum states from initialisation through to readout is very delicate: operating at low temperatures reduces the thermal noise and helps maintain stability, whilst also being required for the superconductivity of the QPU.

In order to realise fault-tolerant quantum computing in solid-state modalities, large-scale cryogenic input-output (IO) infrastructures are required, the likes of which will be significantly larger than those in use today. The IO infrastructure referred to is the input-output (IO) connectivity (control wiring) between the quantum processor, housed in a milli-Kelvin environment, and the control elements which are at room temperature.

The IO scaling required is yet to be demonstrated and presents significant challenges in thermal modelling, hardware design and verification with alternative IO approaches being explored as a result of these scaling requirements. Traditionally, tooling around thermal modelling of cryogenic IO infrastructure relies on linear approximations which do not take into account the complexities and inter-stage dependencies of a cryogenic platform. Work carried out by our Hardware Engineering team sees that linear approximation is only accurate when heat loads are sufficiently small, but as scaling occurs and payload – and therefore heat load – is increased, that a non-linear behaviour is observed, leading to a growing disagreement, resulting in an over or underestimation of payload IO.

Introducing a new approach to thermal modelling of cryogenic IO infrastructure

In our latest preprint, released on arXiv, the Hardware Engineering team at OQC have presented a novel approach to thermally modelling cryogenic platforms with the inclusion of cryogenic infrastructure. The work is presented as a design tool for scaling cryogenic IO platforms for quantum computing.

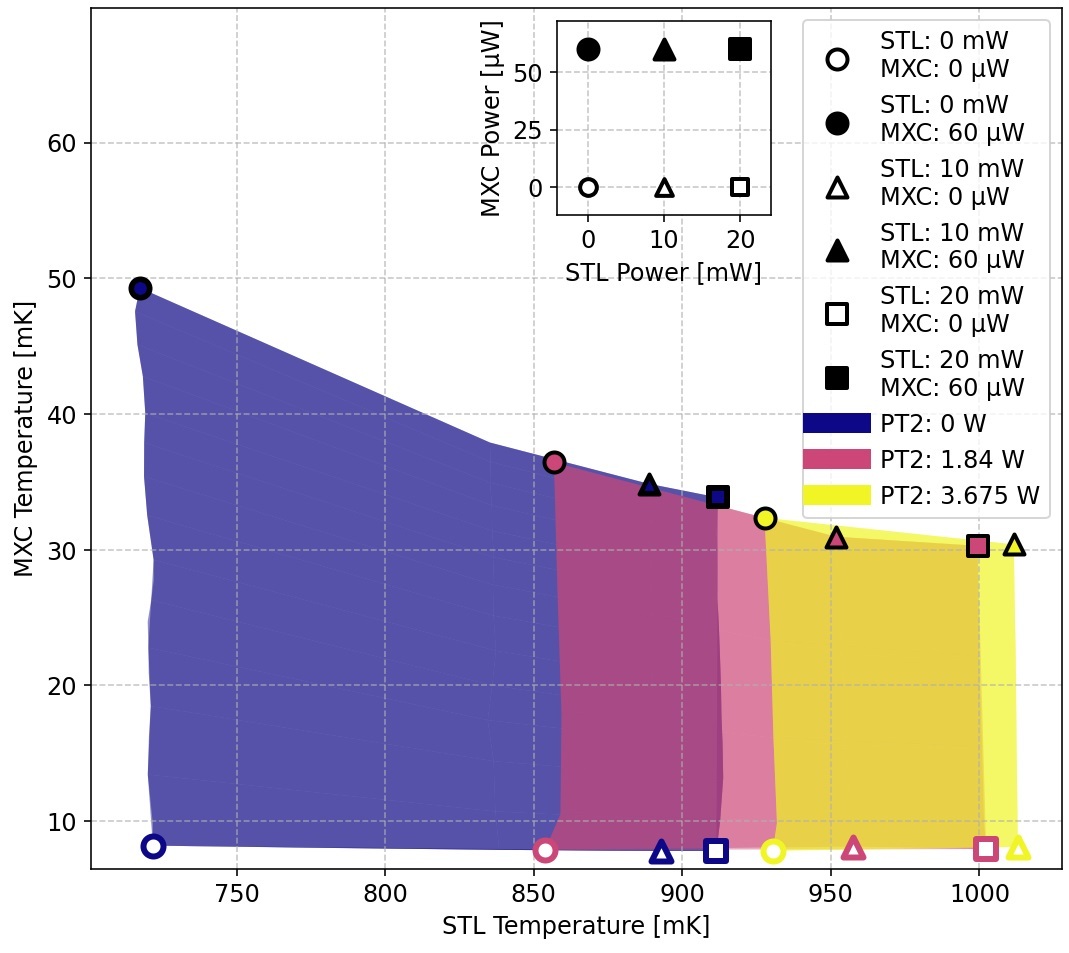

In this novel approach, the team constructed a ‘platform capacity map’ by taking comprehensive measurements across each stage of a commercially available dilution refrigerator. The platform map was obtained by systematically varying the heat applied to each individual stage as a function of the heat applied to every other stage, to form a coordinate system of stage thermal loads. The results collected, quantified the platform’s complex response to heat load distributed over multiple temperature stages, and accounted for inter-stage dependencies. The platform capacity map created therefore allows us to understand how the IO infrastructure affects the cryogenic platforms performance.

The useful application of platform capacity mapping

A distributed heat load presented by a prospective payload can be calculated and inputted directly into the capacity map. This allows for a predictive modelling capability which can be used for any arbitrary payload that fits within the power space covered in the platform capacity map. This method avoids using an analytical model of how the platform responds to the payload and assumptions that come with that approach. We can then use the results to analyse the payloads effect on stage temperatures, pressures or flow rate, and draw conclusions on thermal overheads and bottlenecks on temperature stages. This allows for significant design insight, supporting predictions into how an arbitrary IO infrastructure would affect the platform and allowing for optimisation of the payload and the platform.

Figure 1. Plot shows thermal capacity maps superimposed simulating different IO payloads (blue, purple, yellow). The thermal overhead, essential to understanding the available heat budget such as to correctly design/optimise the payload, can be simply interpreted as bounded by the shaded area of the capacity map for each scenario depending on the designers temperature limits.

The wider impact of platform capacity mapping

The work carried out highlights the benefit of a deeper understanding of cryogenic platforms and the utility of a platform capacity map for insights on system-level overheads and modelling. The approach allows for design confidence and the ability to optimise both the cryogenic platform and IO infrastructure in advance of manufacture and integration.

The technique therefore expands the toolset for manufacturers of components, IO, and quantum computing system designers, to reliably design Large-Scale IO platforms. As this work is relevant to base cryogenic system design, quantum computing systems and other cryogenic devices, the technique should also find ready application within industry with cryogenic OEMs.

Finally, a key extension of this work is applying capacity mapping to more platforms, to better understand its utility and investigate platform-to-platform variance, as well as further verification of its predictive capability with larger validation payload testing.

Read the full preprint on ArXiv

Thermal capacity mapping of cryogenic platforms for quantum computers.

Scott A. Manifold, George B. Long, Jonathan J. Burnett

Join our newsletter for more articles like this

By clicking ‘sign up’ you’re confirming that you agree with our Terms & Conditions