RESEARCH

Cutting-Edge Research By World-Leading Minds

Our research spans the full stack of quantum computing, from materials to qubit designs, control hardware, cryogenics, software and quantum theory.

Nanofabrication & materials science

To build reliable quantum hardware at scale, we need to fabricate stable, long-lived superconducting qubits at high yield.

In a world-first, we achieved through-sapphire machining, enabling us to retain high-quality qubits fabricated on sapphire. This technique advances our ability to scale up the coherence of our devices, and was published in Advanced Materials. We have successfully demonstrated the technique through the complete manufacturing process of our own 32-qubit OQC Toshiko® QPU.

We have created new models to optimise post-fabrication fine-tuning of the Josephson Junction, the core component of a superconducting qubit. We have additionally analysed how different techniques can reveal vital information required for precise manufacturing of Josephson junctions.

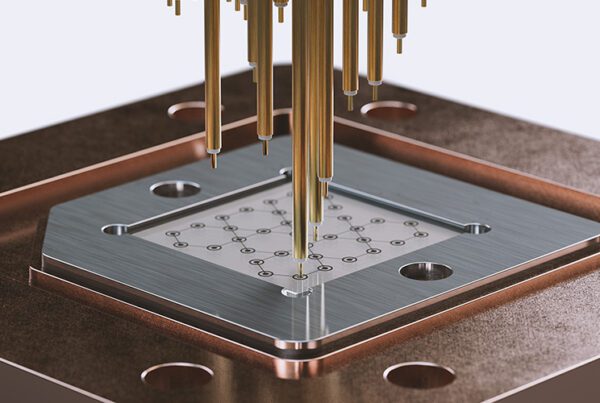

Qubit architecture & design

Taking advantage of the flexibility and simplicity of our core coaxmon architecture, we are designing purpose-built qubits with the properties required for fault-tolerant quantum computing.

We have demonstrated quantum error detection in multi-mode qubits, showing a key step in the novel technology behind our quantum computers. We show significant increases in qubit lifetimes by addressing the largest source of error in superconducting devices on an individual-qubit level. This dual-rail dimon qubit design enables OQC’s strategy for hardware-efficient quantum error correction to realise rapidly scalable, low-error quantum computation.

Useful quantum computing requires both high accuracy and speed. Research from our founder and CSO Peter Leek’s lab demonstrated an industry-leading combination of 25ns two-qubit gate-speed and 99.8% fidelity, by using a smart qubit design developed on our coaxmon technology.

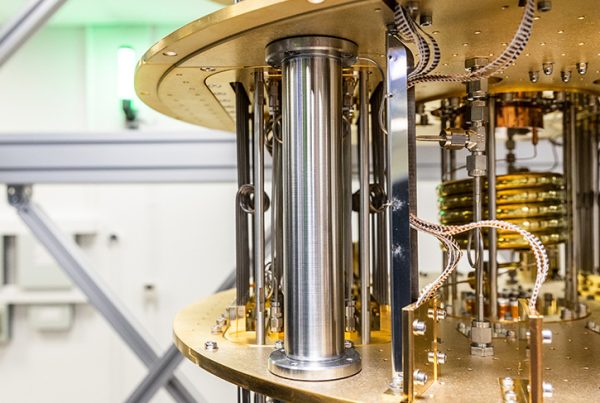

Cryogenics

Superconducting chips need to be kept at temperatures colder than outer space to maintain their coherence. As we scale qubit number and chip size, the cryogenics needs to scale too. Fault tolerant quantum computing will require large-scale cryogenic input-output (IO) infrastructures, which are complex to design, model and validate. In our recent work we demonstrate a design tool for cryogenic platform development, quantifying a platform’s complex responses to heat load distribution and identifying the key bottlenecks to enable scalable cryogenic infrastructure.

YOU MAY ALSO BE INTERESTED IN

The latest in R&D from OQC

TALK TO US

Let’s chat

For more information, or to talk to our team about the most appropriate quantum solution for your needs, get in touch with us today.